# Programmable Low-Jitter Precision CMOSOscillator

## **General Description**

The DSC8101 & DSC8121 series of high performance field-programmable oscillators utilizes a proven silicon MEMS technology to provide excellent jitter and stability over a range of supply voltages temperatures. Using the TIMEFLASH programmer, the end user can easily program the oscillators' frequency in the field for immediate testing or use in advance prototype development or production.

DSC8101 has a standby feature allowing it to completely power-down when EN pin is pulled low; whereas for DSC8121, only the outputs are disabled when EN is low. Both oscillators are available in industry standard packages, including the small 3.2x2.5 mm<sup>2</sup>, and are "drop-in" replacement for standard 4-pin CMOS quartz oscillators.

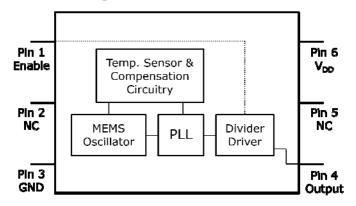

## **Block Diagram**

## **Output Enable Modes**

| EN Pin | DSC8101       | DSC8121         |

|--------|---------------|-----------------|

| High   | Output Active | Output Active   |

| NC     | Output Active | Output Active   |

| Low    | Standby       | Output Disabled |

#### **Features**

- Low RMS Phase Jitter: <1 ps (typ)</li>

- High Stability: ±10, ±25, ±50 ppm

- Wide Temperature Range

- o Automotive: -55° to 125° C

- o Ext. Industrial: -40° to 105° C

- o Industrial: -40° to 85° C

- o Ext. commercial: -20° to 70° C

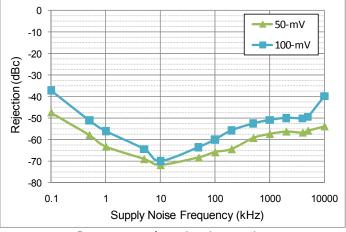

- High Supply Noise Rejection: -50 dBc

- Short Lead Time: 2 Weeks

- Wide Freq. Range: 10 to 170 MHz

- Small Industry Standard Footprints

3.2x2.5, 5.0x3.2, and 7.0x5.0 mm

- Excellent Shock & Vibration Immunity

Oualified to MIL-STD-883

- High Reliability

- o 20x better MTF than quartz oscillators

- Low Current Consumption

- Supply Range of 2.25 to 3.6 V

- Standby & Output Enable Function

- Lead Free & RoHS Compliant

## **Applications**

- Storage Area Networks

- o SATA, SAS, Fibre Channel

- Passive Optical Networks

- o EPON, 10G-EPON, GPON, 10G-PON

- Ethernet

- o 1G, 10GBASE-T/KR/LR/SR, and FCoE

- HD/SD/SDI Video & Surveillance

- PCI Express

- DisplayPort

### **Absolute Maximum Ratings**

| Item           | Min  | Max          | Unit | Condition  |

|----------------|------|--------------|------|------------|

| Supply Voltage | -0.3 | +4.0         | V    |            |

| Input Voltage  | -0.3 | $V_{DD}+0.3$ | V    |            |

| Junction Temp  | -    | +150         | °C   |            |

| Storage Temp   | -55  | +150         | °C   |            |

| Soldering Temp | -    | +260         | °C   | 40sec max. |

| ESD            | -    |              | V    |            |

| НВМ            |      | 4000         |      |            |

| MM             |      | 400          |      |            |

| CDM            |      | 1500         |      |            |

#### Note: 1000+ years of data retention on internal memory

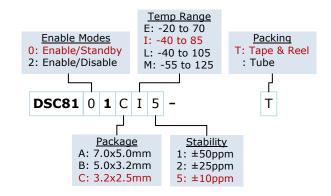

### **Ordering Code**

### **Specifications**

| Parameter                                                                 |                                    | Condition                                                                                    | Min.                 | Тур.               | Max.                      | Unit              |

|---------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|----------------------|--------------------|---------------------------|-------------------|

| Supply Voltage <sup>1</sup>                                               | $V_{DD}$                           |                                                                                              | 2.25                 |                    | 3.6                       | V                 |

| Supply Current                                                            | $I_{DD}$                           | EN pin low – output is disabled<br>DSC8101<br>DSC8121                                        |                      | 20                 | 0.095<br>22               | mA                |

| Frequency Stability Ext Comm. & Ind. only All temp ranges All temp ranges | Δf                                 | Includes frequency variations due<br>to initial tolerance, temp. and<br>power supply voltage |                      |                    | ±10<br>±25<br>±50         | ppm               |

| Aging                                                                     | Δf                                 | 1 year @25°C                                                                                 |                      |                    | ±5                        | ppm               |

| Startup Time <sup>2</sup>                                                 | t <sub>su</sub>                    | T=25°C                                                                                       |                      |                    | 5                         | ms                |

| Input Logic Levels Input logic high Input logic low                       | $oldsymbol{V}_{IH}$                |                                                                                              | 0.75xV <sub>DD</sub> |                    | -<br>0.25xV <sub>DD</sub> | V                 |

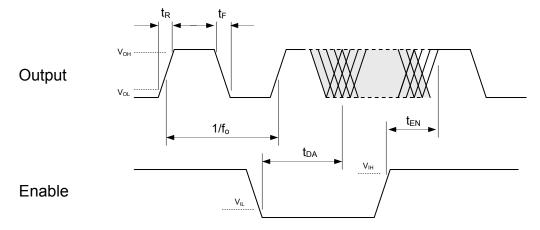

| Output Disable Time <sup>3</sup>                                          | $t_DA$                             |                                                                                              |                      |                    | 5                         | ns                |

| Output Enable Time                                                        | t <sub>EN</sub>                    | DSC8101<br>DSC8121                                                                           |                      |                    | 5<br>20                   | ms<br>ns          |

| Enable Pull-Up Resistor <sup>4</sup>                                      |                                    | Pull-up resistor exist                                                                       |                      | 40                 |                           | kΩ                |

|                                                                           |                                    | CMOS Output                                                                                  |                      |                    |                           |                   |

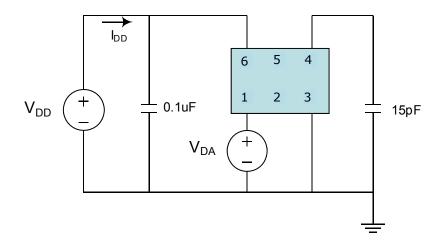

| Supply Current <sup>4</sup>                                               | $I_{DD}$                           | output is enabled $C_L=15$ pF, $F_0=125$ MHz                                                 |                      | 31                 | 35                        | mA                |

| Output Logic Levels<br>Output logic high<br>Output logic low              | V <sub>OH</sub><br>V <sub>OL</sub> | I=±6mA                                                                                       | 0.9xV <sub>DD</sub>  |                    | -<br>0.1xV <sub>DD</sub>  | V                 |

| Output Transition time <sup>3</sup> Rise Time Fall Time                   | t <sub>R</sub><br>t <sub>F</sub>   | 20% to 80%<br>C <sub>L</sub> =15pF                                                           |                      | 1.1<br>1.3         | 2<br>2                    | ns                |

| Frequency                                                                 | $f_0$                              | All temp range except Auto<br>Auto temp range                                                | 10                   |                    | 170<br>100                | MHz               |

| Output Duty Cycle                                                         | SYM                                |                                                                                              | 45                   |                    | 55                        | %                 |

| Period Jitter                                                             | $J_{PER}$                          | Fout=125MHz                                                                                  |                      | 3                  |                           | ps <sub>RMS</sub> |

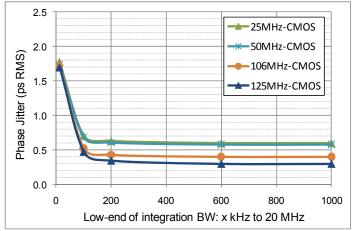

| Integrated Phase Noise                                                    | ${\sf J}_{\sf PH}$                 | 200kHz to 20MHz @ 125MHz<br>100kHz to 20MHz @ 125MHz<br>12kHz to 20MHz @ 125MHz              |                      | 0.3<br>0.38<br>1.7 | 2                         | ps <sub>RMS</sub> |

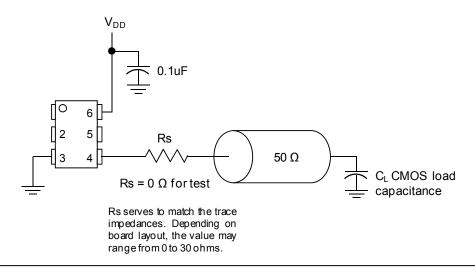

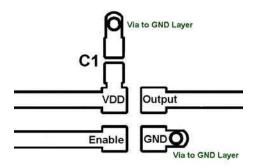

- Pin 6  $V_{DD}$  should be filtered with 0.1uf capacitor.  $t_{su}$  is time to 100PPM of output frequency after  $V_{DD}$  is applied and outputs are enabled. Output Waveform and Test Circuit figures below define the parameters.

- Output is enabled if pad is floated or not connected.

## Nominal Performance Parameters (Unless specified otherwise: T=25° C, V<sub>DD</sub>=3.3 V)

Phase jitter (integrated phase noise)

Power supply rejection ratio

## **Output Waveform**

## **Typical Termination Scheme**

### **Test Circuit**

## **Board Layout (recommended)**

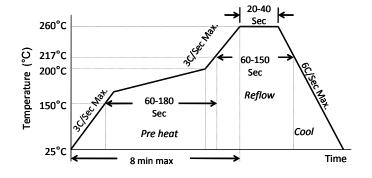

#### **Solder Reflow Profile**

| MSL 1 @ 260°C refer to JSTD-020C  |              |  |

|-----------------------------------|--------------|--|

| Ramp-Up Rate (200°C to Peak Temp) | 3°C/Sec Max. |  |

| Preheat Time 150°C to 200°C       | 60-180 Sec   |  |

| Time maintained above 217°C       | 60-150 Sec   |  |

| Peak Temperature                  | 255-260°C    |  |

| Time within 5°C of actual Peak    | 20-40 Sec    |  |

| Ramp-Down Rate                    | 6°C/Sec Max. |  |

| Time 25°C to Peak Temperature     | 8 min Max.   |  |

Page 4 |

## **Package Dimensions**

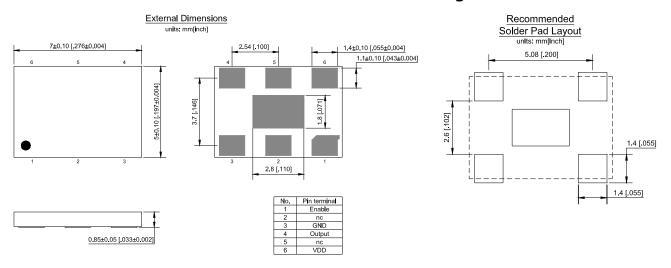

#### 7.0 x 5.0 mm Plastic Package

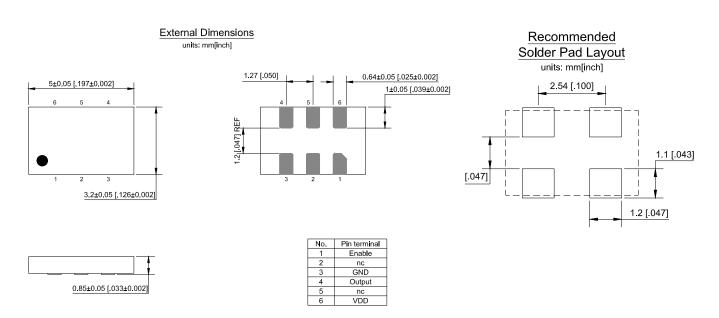

#### 5.0 x 3.2 mm Plastic Package

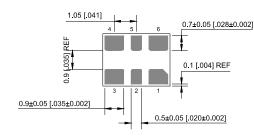

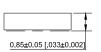

### 3.2 x 2.5 mm Plastic Package

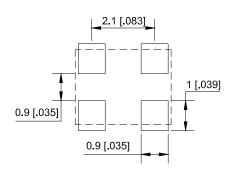

### Recommended Solder Pad Layout units: mm[inch]

| No. | Pin terminal |

|-----|--------------|

| 1   | Enable       |

| 2   | nc           |

| 3   | GND          |

| 4   | Output       |

| 5   | nc           |

| 6   | VDD          |

DISCERA, Inc. Phone: +1 (408) 432-8600 1961 Concourse Drive,

San Jose, California Fax: +1 (408) 432-8609 • Email: sales@discera.com

95131

USA www.discera.com